# DESIGN, SYNTHESIS AND APPLICATION OF REVERSIBLE LOGIC ARCHITECTURES FOR ENERGY AWARE SUSTAINABLE COMPUTING

A Thesis Submitted In Partial Fulfillment of the Requirements for the Degree of

# DOCTOR OF PHILOSOPHY in COMPUTER SCIENCE AND ENGINEERING

by

# NIRUPMA PATHAK

(MUIT0118190002)

Under the Supervision of

Dr. Santosh Kumar

Associate Professor,

Department of Computer Engineering & Information Technology MAHARISHI UNIVERSITY OF INFORMATION TECHNOLOGY, LUCKNOW,

of the

FACULTY OF ENGINEERING AND TECHNOLOGY MAHARISHI UNIVERSITY OF INFORMATION TECHNOLOGY, LUCKNOW, JANUARY-2023

# **Candidate's Declaration**

I hereby declare that the work presented in this thesis entitled **DESIGN**, **SYNTHESIS AND APPLICATION OF REVERSIBLE LOGIC ARCHITECTURES FOR ENERGY AWARE SUSTAINABLE COMPUTING.** in fulfillment of the requirements for the award of Degree of Doctor of Philosophy submitted in School of Engineering &Technology, Maharishi University of Information Technology, Lucknow is an authentic record of my own research work carried out under the supervision of **Dr. Santosh Kumar (Associate Professor)**, **Department of Computer Engineering & Information Technology** in this University. I also declare that the work embodied in the present thesis

- i) Is my original work and has not been copied from any journal/ thesis/ book; and

- ii) Has not been submitted by me for any other Degree or Diploma of any University/ Institution.

Date -

( Nirupama Pathak) Enrollment No. : **MUIT0118190002** Research Scholar

#### CERTIFICATE

It has been confirmed that Nirupma Pathak (MUIT0118190002) has carried out the research presented in this thesis entitled "DESIGN, SYNTHESIS AND APPLICATION OF **REVERSIBLELOGIC ARCHITECTURES FOR ENERGY AWARE SUSTAINABLE** COMPUTING" under my supervision at Maharishi University of Information Technology, Lucknow. The contents of the thesis do not constitute the basis for the award of any other degree to the candidate or to anyone else from this or any other University/Institution.

Dr. Santosh Kumar Assoc. Prof.,

CE and IT

# MAHARISHI UNIVERSITY OF INFORMATION TECHNOLOGY, LUCKNOW,

Date: 01-01-2023

# TABLE OF CONTENTS

| P                                                                                                                                 | age No. |

|-----------------------------------------------------------------------------------------------------------------------------------|---------|

| Certificate                                                                                                                       | i       |

| Abstract                                                                                                                          | ii      |

| Acknowledgements                                                                                                                  | iv      |

| Dedication                                                                                                                        | v       |

| Table of Contents                                                                                                                 | vi      |

| List of Tables                                                                                                                    |         |

| ix                                                                                                                                |         |

| List of Figures                                                                                                                   |         |

| xi                                                                                                                                |         |

| List of Symbols and Abbreviations                                                                                                 | xiii    |

| CHAPTER 1: INTRODUCTION                                                                                                           | 1-4     |

| INTRODUCTION                                                                                                                      | 1       |

| MOTIVATION                                                                                                                        | 2       |

| OBJECTIVE                                                                                                                         | 2       |

| METHODOLOGIES OF THE RESEARCH                                                                                                     | 3       |

| THESIS ORGANIZATION                                                                                                               | 3       |

| 1.4 CONCLUSION                                                                                                                    | 4       |

| CHAPTER 2: FUNDAMENTAL AND STATE-OF-ART-WORK                                                                                      | 5-19    |

| FUNDAMENTAL OF GDI, REVERSIBILITY CONCEPT, QUANTUM<br>TECHNOLOGY, QCA AND NANOMAGNETIC TECHNOLOGY<br>Basics of GDI-CMOD Technique | 5<br>6  |

| Implementation of Different Functions using GDI-CMOS Technique                                                                    | ue 6    |

| Comparison between GDI-CMOS and conventional CMOS logic g                                                                         | ates 7  |

| transistors                                                                                                                       |         |

| Fundamentals of Reversible Computing<br>Logical-Reversibility                                                                     | 7<br>9  |

| Physical-Reversibility                                                                                                            | 9       |

| Quantum Technology and Quantum gates                                                                                              | 10      |

| Fundamentals of QCA Technology                                                                                                    | 11      |

| Fundamentals of Nano-magnetic Logic                                                                                               | 16      |

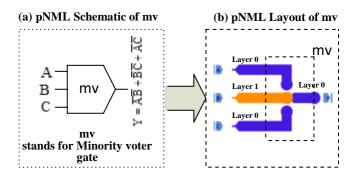

| Architecture of Minority voter gate                                                                                               | 17      |

| STATE-OF-THE-ART WORK                                                                               | 18   |

|-----------------------------------------------------------------------------------------------------|------|

| CONTRIBUTION OF THE DISSERTATION CONTEXT                                                            | 19   |

| CHAPTER 3: CONSERVATIVE REVERSIBLE LOGIC MULTIPLEXER<br>CIRCUITS                                    |      |

|                                                                                                     | 0-29 |

| RELATED WORK ON CONSERVATIVE MULTIPLEXER CIRCUITS<br>CONTRIBUTION TOWARDS THE DESIGN OF MULTIPLEXER | 20   |

| CIRCUITS                                                                                            | 21   |

| THE PROPOSED MULTIPLEXER BASED ON NEW REVERSIBLE                                                    |      |

| GATE                                                                                                | 21   |

| Existing conservative, reversible gates                                                             | 21   |

| Modular approaches to design a multiplexer                                                          | 22   |

| The suggested conservative reversible multiplexer (R-CQCA) gat                                      | te's |

| layout design in QCA technology                                                                     | 26   |

| Table 3.3 compare multiplexers                                                                      | 28   |

| 3.4 CONCLUSIONS REMARKS                                                                             | 29   |

| CHAPTER 4: CONTENT ADDRESSABLE MEMORY (CAM) DESIGN USING QO                                         | CA   |

| AND p-NML TECHNOLOGY 30                                                                             | 0-56 |

| STATE-OF-THE-ART WORK FOR CAM MEMORY                                                                | 31   |

| Prior Work of CAM Memory Using QCA Technology                                                       | 31   |

| Prior Work of CAM Memory Using p-NML Technology                                                     | 33   |

| The Proposed Work Related To CAM Memory Using QCA Technology                                        | 34   |

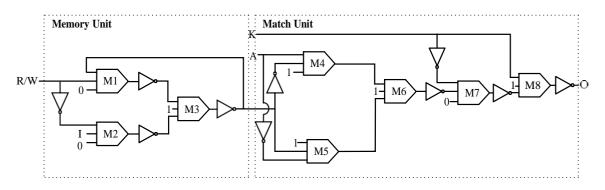

| Memory Unit                                                                                         | 35   |

| Match Unit                                                                                          | 36   |

| GDI-CMOS Based Proposed CAM ell                                                                     | 36   |

| QCA Based Proposed CAM Cell                                                                         | 38   |

| Energy Dissipation Analysis of QCA Based CAM Memory                                                 | 42   |

| Temperature versus Polarization Analysis of The Proposed CAM                                        |      |

| Cell                                                                                                | 44   |

| The Performance Parameter Comparison between Proposed CAM                                           | Л    |

| Cell Using GDI-CMOS and QCA Technology<br>(vi)                                                      | 44   |

| THE PROPOSED WORK RELATED TO CAM MEMORY USING pl             | ١ML      |

|--------------------------------------------------------------|----------|

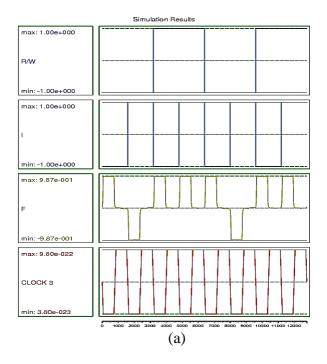

| TECHNOLOGY                                                   | 48       |

| The Proposed Matching Logic Gate<br>The Proposed Memory Unit | 48<br>50 |

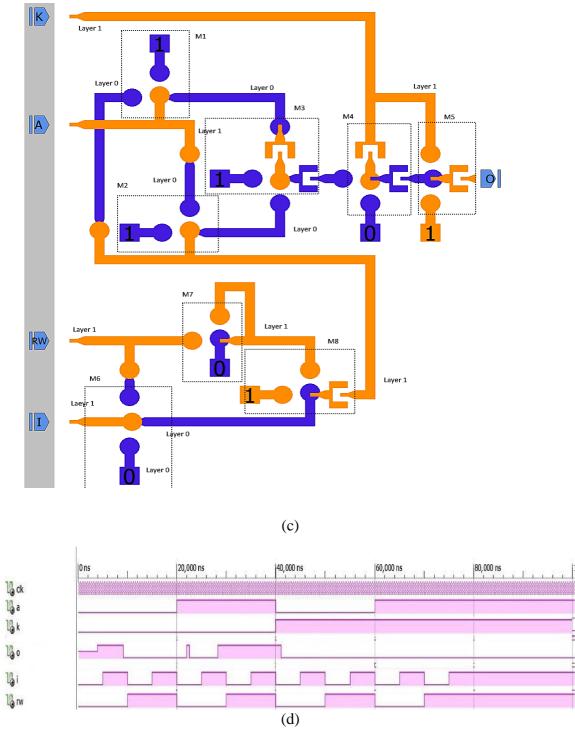

| 4.3.3. The proposed Content Address Memory (CAM) structure   | 53       |

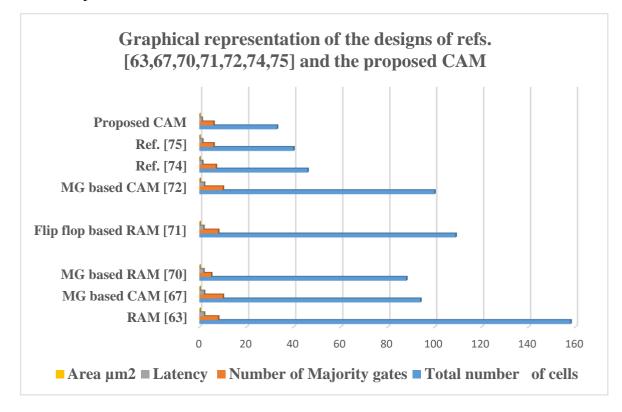

| 4. 4 COMPARATIVE RESULT ANALYSIS                             | 55       |

| 4.5 CONCLUSION REMARKS                                       | 56       |

# CHAPTER 5: DIGITAL CIRCUITS USING 3D NANO-MAGNETIC LOGICARCHITECTURES57-76

| THE PROPOSED DIGITAL CIRCUIT MODELS                                                                                                           | 59             |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

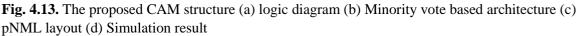

| Design of Ex-OR Gate                                                                                                                          | 59             |

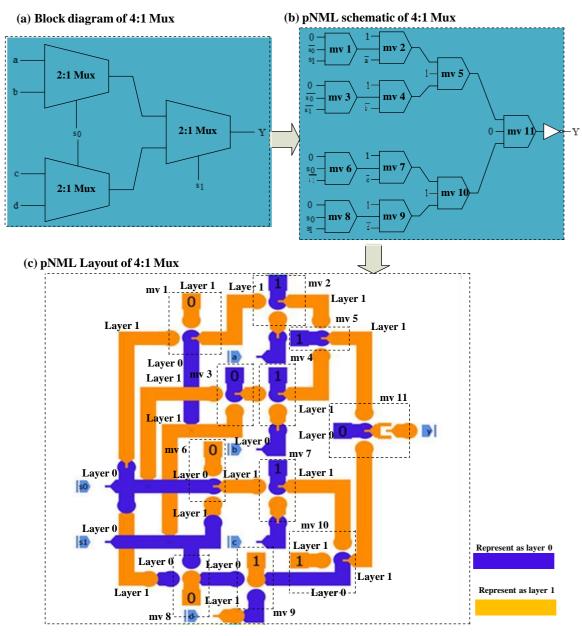

| The p-NML Technology-based PG                                                                                                                 | 60             |

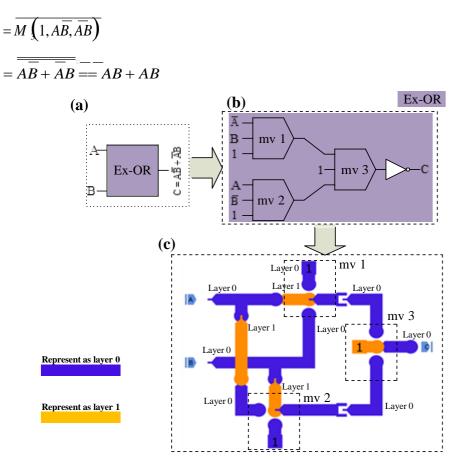

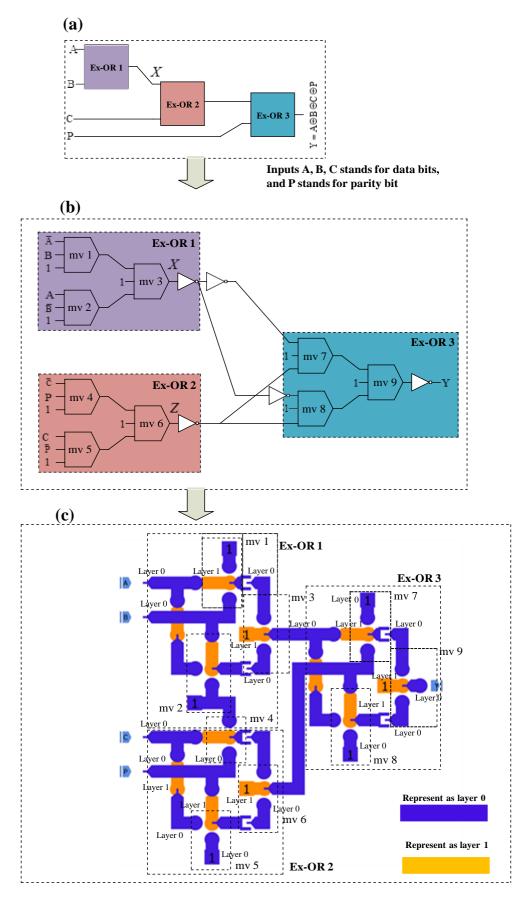

| Even-Parity Checker design                                                                                                                    | 63             |

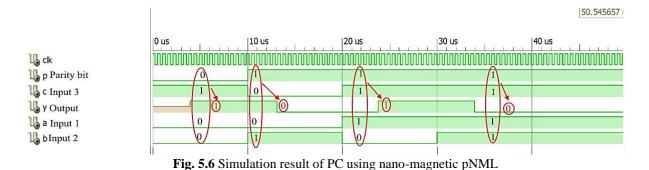

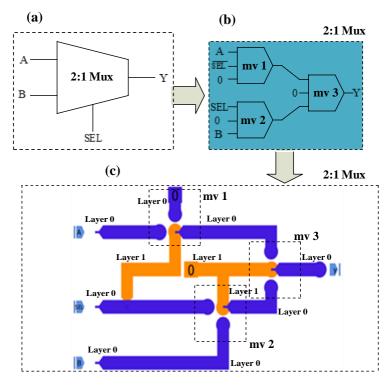

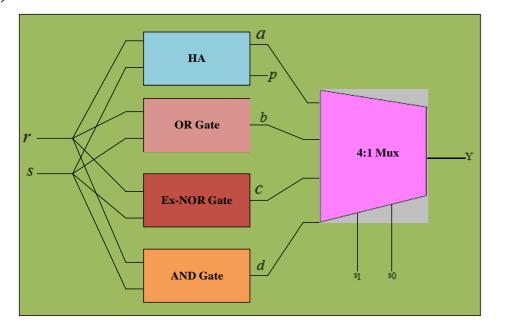

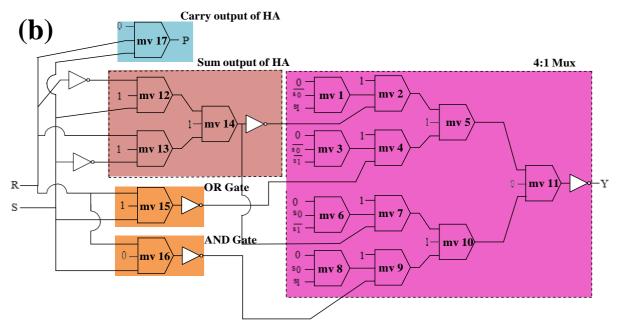

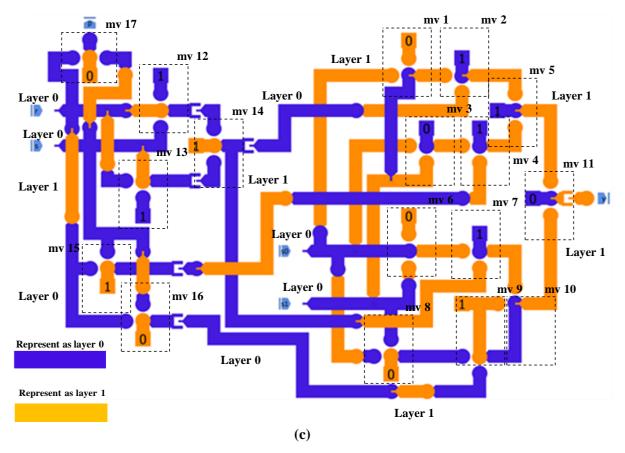

| Results of the PG and PC Circuits in comparison to existing<br>The new Multiplexer design<br>The pNML technology 4:1 multiplexer architecture | 66<br>67<br>69 |

| Comparative results of multiplexer circuits                                                                                                   | 71             |

| The proposed design of ALU                                                                                                                    | 71             |

| Performance of ALU circuits                                                                                                                   | 75             |

| CONCLUSION REMARKS                                                                                                                            | 75             |

| CHAPTER 6: CONCLUSIONS AND FUTURE SCOPE | 77-78 |

|-----------------------------------------|-------|

| References                              | 79-86 |

| List of Publications                    | 94    |

# LIST OF TABLES

| Table No.  | Title                                                                                       | Page<br>No. |

|------------|---------------------------------------------------------------------------------------------|-------------|

| 2.1<br>2.2 | Generating of basic operations using the GDI cell<br>The truth table of minority voter gate | 7<br>18     |

| 3.1        | Data output from a mux 4:1                                                                  | 23          |

| 3.2        | Data output from a mux 8:1                                                                  | 23          |

| 3.3        | Comparative result of Mux                                                                   | 27          |

| 3.4        | Analyses of the suggested multiplexer's performance metrics                                 | 28          |

| 3.5        | New multiplexer with the prior design of multiplexer                                        | 29          |

| 4.1        | CAM functions                                                                               | 35          |

| 4.2        | Memory functions                                                                            | 36          |

| 4.3        | Default parameter values while simulating in QCADesigner software                           | 42          |

| 4.4        | Energy Analysis Simulation Conditions                                                       | 43          |

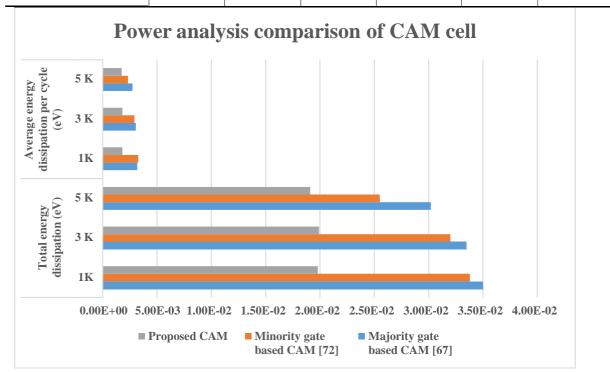

| 4.5        | Power analysis comparison of Proposed CAM cell based on QCA technology with prior works     | 43          |

| 4.6        | Parametric analysis of proposed structures using GDI-CMOS technology                        | 44          |

| 4.7        | Parametric analysis of proposed structures using QCA technology                             | 45          |

| 4.8        | Performance comparison between proposed CAM cells based on GDI-CMOS and QCA technology      | 45          |

| 4.9        | Comparison of the newly memory and match cell with other published works                    | 46          |

| 4.10       | Performance Comparison of proposed CAM cell based on QCA technology compared to prior works | 46          |

| 4.11       | CAM unit                                                                                    | 50          |

| 4.12 | CAM-memory unit Truth table                                             | 52 |

|------|-------------------------------------------------------------------------|----|

| 4.13 | CAM unit analysis table                                                 | 55 |

| 4.14 | The suggested CAM design is compared to current QCA and CMOS technology | 56 |

| 5.1  | Computational Table of Ex-OR gate                                       | 60 |

| 5.2  | PG circuit with latency analysis                                        | 63 |

| 5.3  | Computational table of PC circuit                                       | 64 |

| 5.4  | Parameters comparison analysis of Parity generator and checker circuit  | 66 |

| 5.5  | Latency analysis of 2:1 multiplexer                                     | 68 |

| 5.6  | Truth table of 4 to 1 multiplexer                                       | 69 |

| 5.7  | Latency of 4:1 mux                                                      | 69 |

| 5.8  | Comparison of new multiplexer design with literature designs            | 71 |

| 5.9  | Computational table of ALU                                              | 74 |

| 5.10 | Comparative analysis results of ALU                                     | 75 |

## LIST OF FIGURES

| Figure No. | Title of Figure                                                                                                                                                                                                                   | Page<br>No. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.1        | Schematic of basic GDI-CMOS based gate                                                                                                                                                                                            | 6           |

| 2.2        | NoT needed for GDI-CMOS and conventional CMOS based logic technique                                                                                                                                                               | 7           |

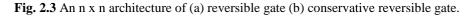

| 2.3        | An n x n architecture of (a) reversible gate (b) conservative reversible gate.                                                                                                                                                    | 8           |

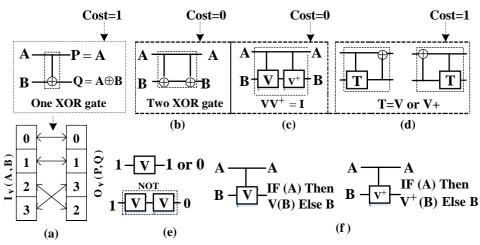

| 2.4        | Basic of Quantum cost                                                                                                                                                                                                             | 9           |

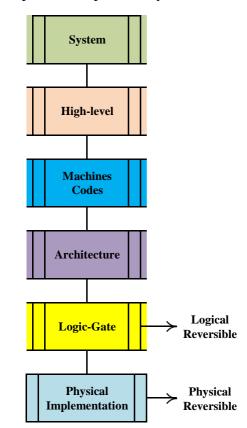

| 2.5        | Logical and Physical reversible approach in digital hardware system                                                                                                                                                               | 10          |

| 2.6        | Basic QCA Cell (90 <sup>0</sup> cell)                                                                                                                                                                                             | 12          |

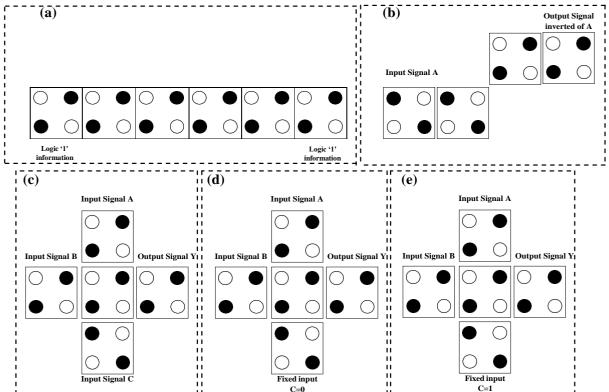

| 2.7        | Basic types of QCA technology (a) QCA wire $(90^0)$ (b) QCA<br>Inverter (c) Input Majority Gate (d) 2 input QCA AND Gate<br>realized using 3- input Majority Gate (e) Input QCA OR Gate<br>realized using 3 inputs Majority Gate. | 12          |

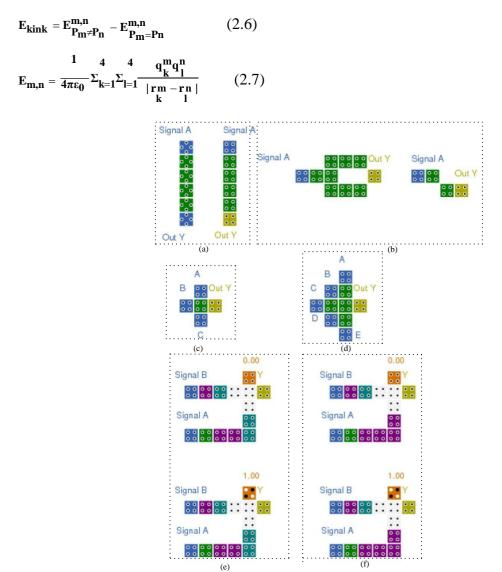

| 2.8        | A component of QCA (a) Rotation based $45^{0}$ and $90^{0}$ wires (b)<br>Inverter (c) 3-input Majority Gate (d) 5-input majority gate (e)<br>Synchronized AND, OR gate (f) Unsynchronized AND, OR gate.                           | 14          |

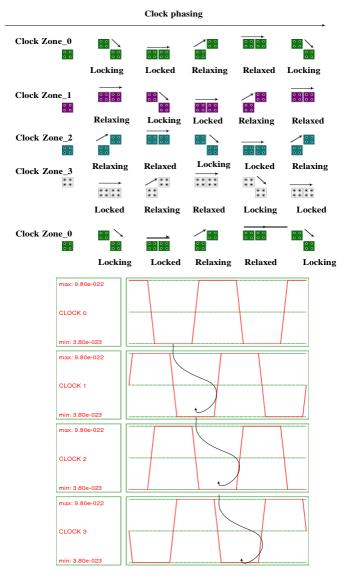

| 2.9        | Four-phase clock in QCA                                                                                                                                                                                                           | 15          |

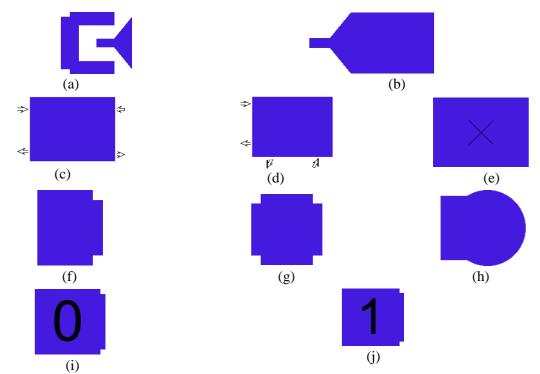

| 2.10       | Elements (a) inverter (b) ANC (c) Domain wall (d) corner (e) via type (f) t type (g) x connection (h) pad type (i) fixed '0' (j) fixed '1'                                                                                        | 17          |

| 2.11       | Minority voter gate schematic and layout                                                                                                                                                                                          | 18          |

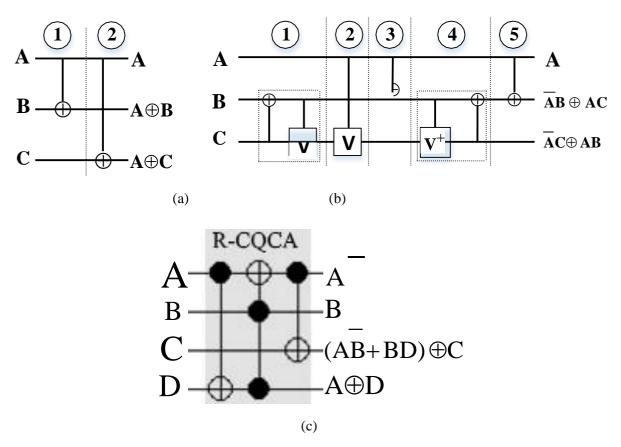

| 3.1        | Quantum circuit of (a) F2G (b) FRG (c) R-CQCA                                                                                                                                                                                     | 22          |

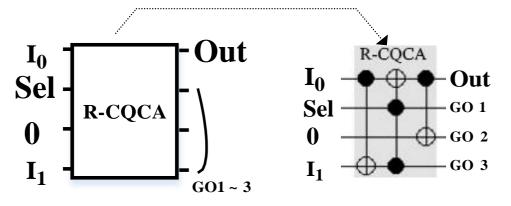

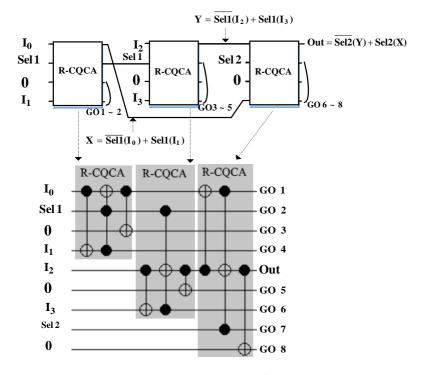

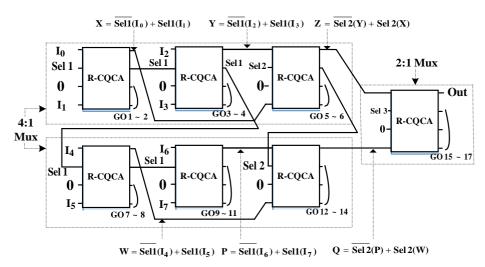

| 3.2        | The proposed design of reversible multiplexer                                                                                                                                                                                     | 24          |

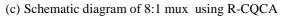

| 3.3        | Physical design                                                                                                                                                                                                                   | 27          |

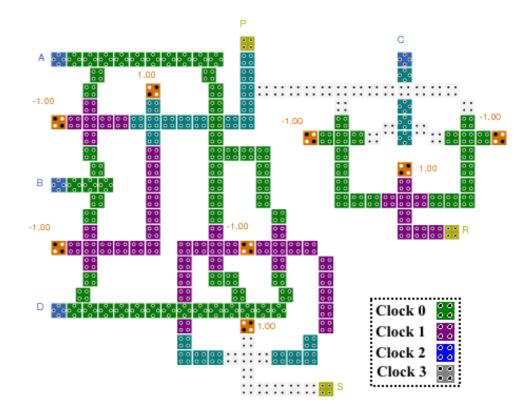

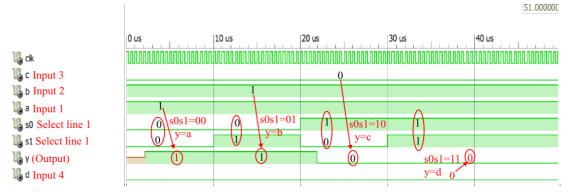

| 3.4        | The outcome of a 2:1 multiplexer simulation using R-CQCA                                                                                                                                                                          | 28          |

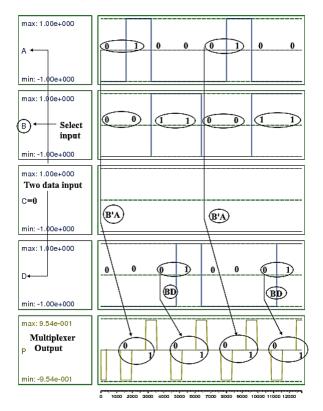

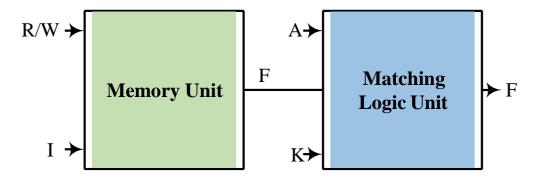

| 4.1        | CAM cell architecture (a) Block representation (b) Logic circuit                                                                                                                                                                  | 34          |

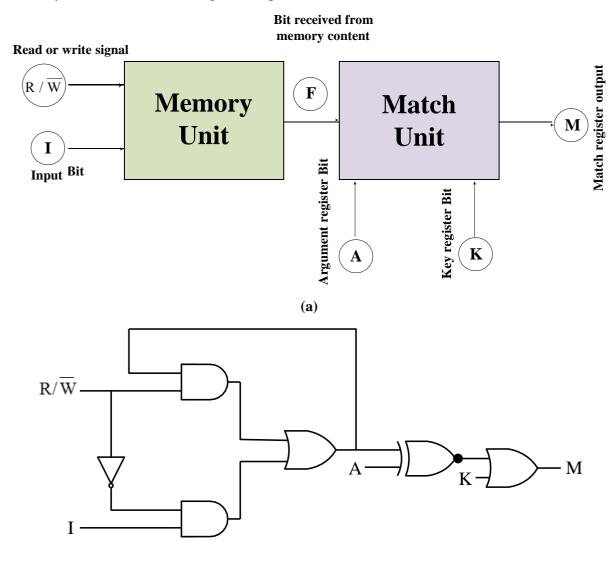

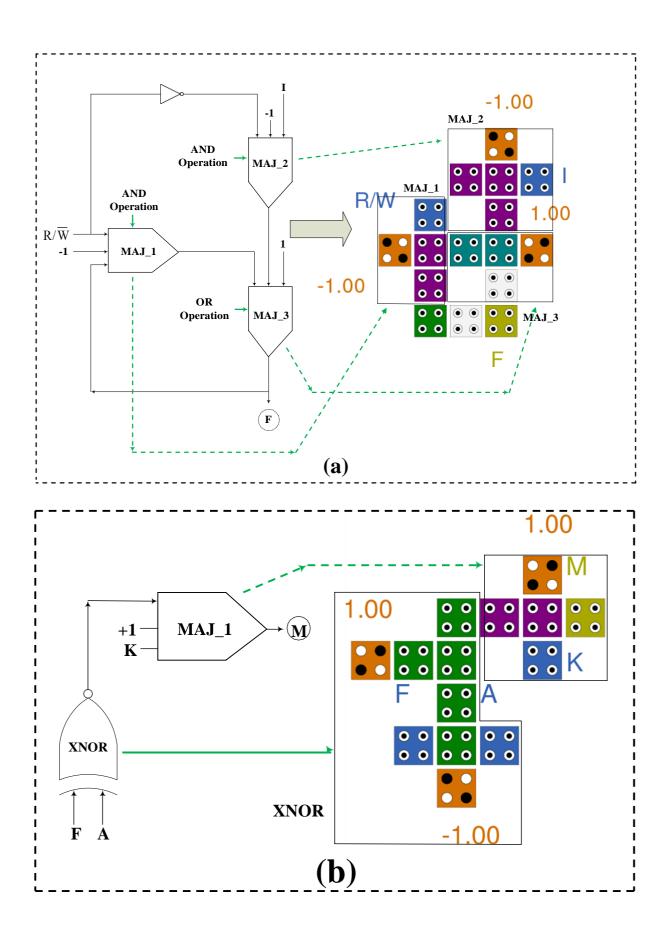

| 4.2        | CAM cell modules (a) Memory operation unit of a single layer<br>CAM cell logic circuit (b) Match unit of a single layer CAM cell<br>logic circuit                                                                                 | 35          |

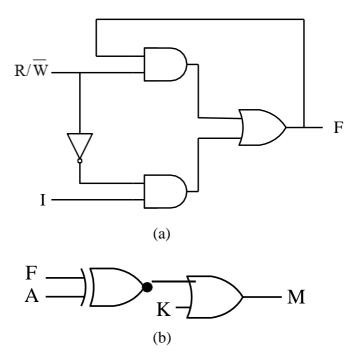

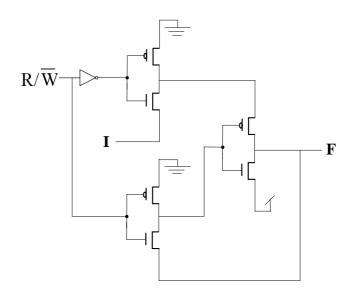

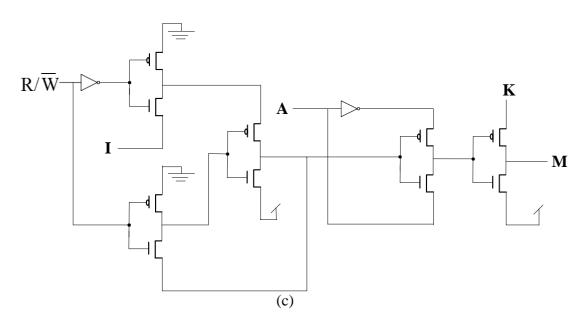

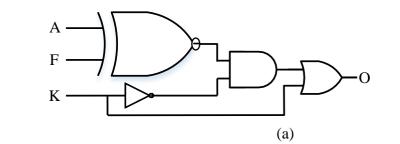

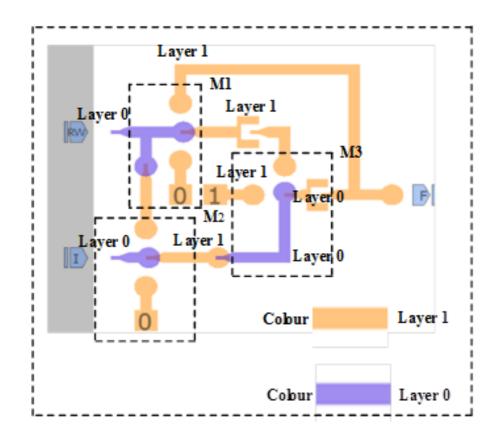

| 4.3        | Design of proposed structures using the GDI-CMOS technique<br>(a) Memory operation unit, (b) Match operation unit, (c) CAM cell                                                                                                   | 37          |

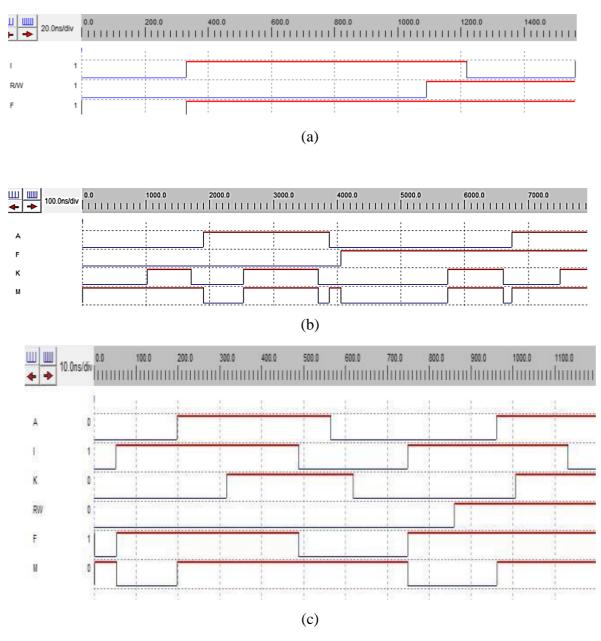

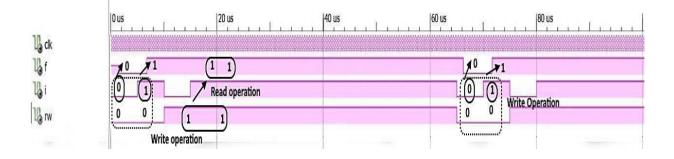

| 4.4        | Simulations of proposed structures using the GDI-CMOS techniqu<br>(a) Proposed Memory operation unit, (b) Proposed Match operatio<br>unit, (c) Proposed CAM cell                                                                  | 38          |

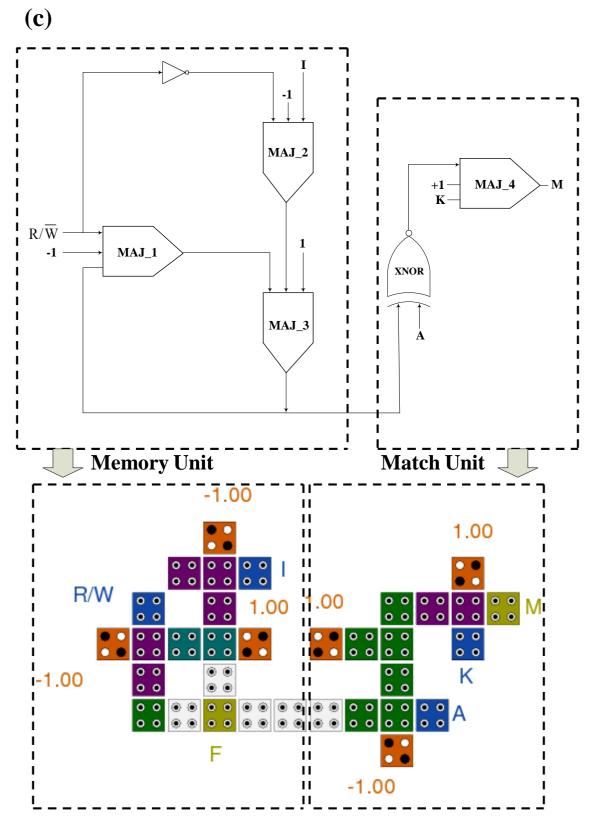

| 4.5        | Design of proposed schematic and layout using a QCA technique<br>(a) Memory operation unit, (b) Match operation unit, (c) CAM cell                                                                                                | 40          |

| 4.6        | Simulations of proposed structures using a QCA technique (a)<br>Memory operation unit (b) Match operation unit, (c) CAM cell                                                                                                      | 42          |

| 4.7  | Graphical Representation of energy analysis, comparison of<br>proposed CAM cell based on QCA technology with prior works<br>[12,19] | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

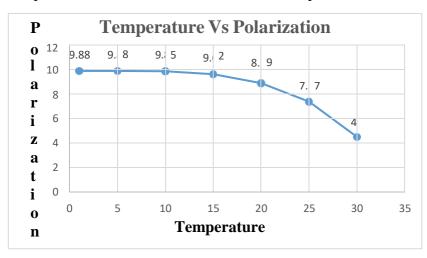

| 4.8  | Temperature deviation with Polarization graph for Proposed QCA-CAM                                                                  | 44 |

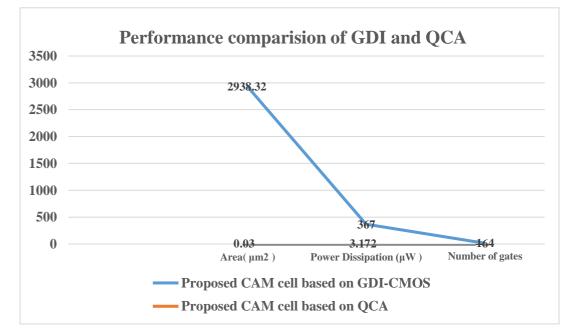

| 4.9  | Graphical representation of Performance Comparison between<br>Proposed CAM cell Based on GDI-CMOS and QCA technology                | 45 |

| 4.10 | Graphical representation of performance comparison between<br>newly CAM cell based on GDI-CMOS and QCA Technology                   | 47 |

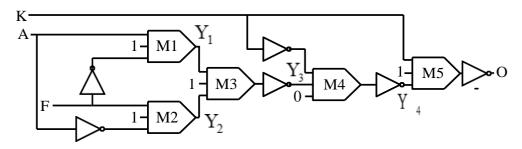

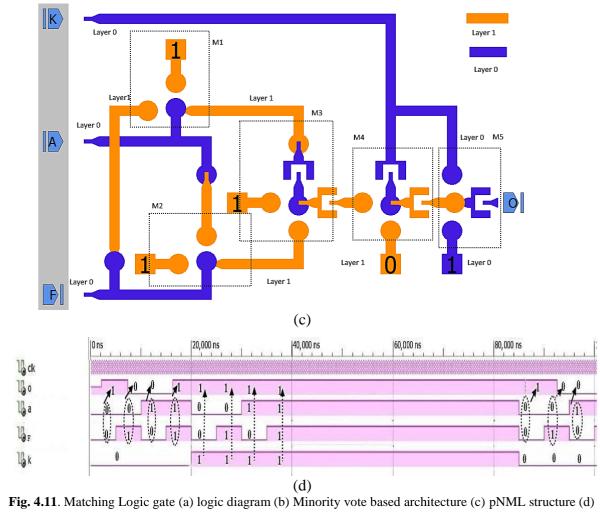

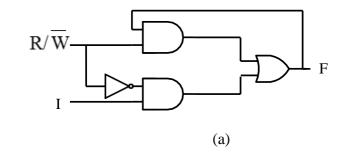

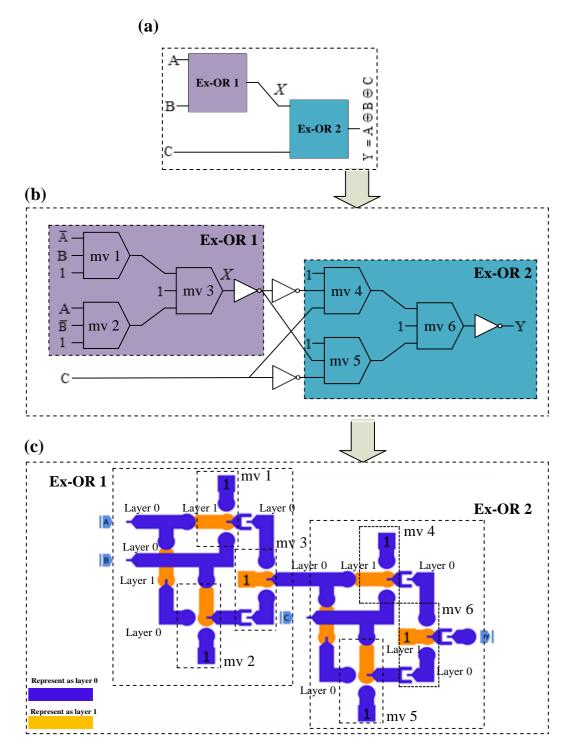

| 4.11 | Matching unit (a) logic (b) Minority (c) structure (d) outcomes                                                                     | 50 |

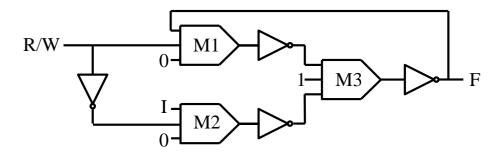

| 4.12 | Memory (a) logic-level (b) Minority (c) structure (d) outcomes                                                                      | 52 |

| 4.13 | The new CAM (a) logic (b) Minority (c) layout (d) outcomes                                                                          | 54 |

| 5.1  | New Ex-OR gate (a) Schematic (b) pNML (c) Physical design                                                                           | 60 |

| 5.2  | Outcomes of the Ex-OR                                                                                                               | 60 |

| 5.3  | New PG (a) Schematic (b) block diagram (c) architecture                                                                             | 62 |

| 5.4  | Simulation result of PG using nano-magnetic pNML                                                                                    | 63 |

| 5.5  | The new PC circuit (a) Block diagram (b) schematic (c) physical design                                                              | 65 |

| 5.6  | Simulation result of PC using nano-magnetic pNML                                                                                    | 66 |

| 5.7  | The proposed 2:1 mux circuit (a) Block diagram (b) schematic (c) physical design                                                    | 68 |

| 5.8  | Simulation result of 2:1 mux using nano-magnetic pNML                                                                               | 68 |

| 5.9  | The new 4:1 mux circuit (a) Block diagram (b) schematic (c) Layout                                                                  | 70 |

| 5.10 | Simulation result of 4 to 1 mux using nano magnetic pNML                                                                            | 70 |

| 5.11 | The new ALU (a) Block diagram (b) schematic(c) physical                                                                             | 74 |

| 5.12 | Simulation result of ALU using nano-magnetic pNML technology                                                                        | 74 |

|      |                                                                                                                                     |    |

# List of Symbols and Abbreviations

| Symbol/Abbreviation | Representation/Explanation                         |

|---------------------|----------------------------------------------------|

| VLSI                | Very large-scale integration                       |

| NoT                 | number of transistors                              |

| GDI                 | Gate diffusion input                               |

| CMOS                | Complementary metal oxide semiconductor            |

| mv                  | minority voter                                     |

| F2G                 | Feynman double gate                                |

| R-CQCA              | Reversible-Conservative quantum-cellular- automata |

| CNOT                | controlled NOT gate                                |

| TG                  | Toffoli Gate                                       |

| FRG                 | Fredkin Gate                                       |

| GC                  | Gate count                                         |

| GO                  | Garbage output                                     |

| QC                  | Quantum cost                                       |

| UD                  | Unit delay                                         |

| RAM                 | Random access memory                               |

| QCA                 | Quantum dot cellular automata                      |

| CAM                 | Content-addressable memory                         |

| NML                 | Nanomagnetic Logic                                 |

| pNML                | Perpendicular nano-magnetic Logic                  |

| iNML                | in-plane nano-magnetic Logic                       |

| PMA                 | perpendicular magnetic anisotropy                  |

| MAJ                 | Majority Gate                                      |

| R/W                 | Read/Write                                         |

| EDA                 | Electronic design automation                       |

| ALU                 | Arithmetic logic unit:                             |

| PG                  | Parity Generator                                   |

| PC                  | Parity Checker                                     |

| VH                  | Very high                                          |

| NI                  | No improvement                                     |

| PG\ PC              | Parity generator\ parity checker                   |

| Ex-OR               | Exclusive OR                                       |

## LIST OF TABLES

| Table No. | Title                                                                                       | Page<br>No. |

|-----------|---------------------------------------------------------------------------------------------|-------------|

| 2.1       | Generating of basic operations using the GDI cell                                           | 7           |

| 2.2       | The truth table of minority voter gate                                                      | 18          |

| 3.1       | Data output from a mux 4:1                                                                  | 23          |

| 3.2       | Data output from a mux 8:1                                                                  | 23          |

| 3.3       | Comparative result of Mux                                                                   | 27          |

| 3.4       | Analyses of the suggested multiplexer's performance metrics                                 | 28          |

| 3.5       | New multiplexer with the prior design of multiplexer                                        | 29          |

| 4.1       | CAM functions                                                                               | 35          |

| 4.2       | Memory functions                                                                            | 36          |

| 4.3       | Default parameter values while simulating in QCADesigner software                           | 42          |

| 4.4       | Energy Analysis Simulation Conditions                                                       | 43          |

| 4.5       | Power analysis comparison of Proposed CAM cell based on QCA technology with prior works     | 43          |

| 4.6       | Parametric analysis of proposed structures using GDI-CMOS technology                        | 44          |

| 4.7       | Parametric analysis of proposed structures using QCA technology                             | 45          |

| 4.8       | Performance comparison between proposed CAM cells based on GDI-CMOS and QCA technology      | 45          |

| 4.9       | Comparison of the newly memory and match cell with other published works                    | 46          |

| 4.10      | Performance Comparison of proposed CAM cell based on QCA technology compared to prior works | 46          |

| 4.11      | CAM unit                                                                                    | 50          |

| 4.12 | CAM-memory unit Truth table                                             | 52 |

|------|-------------------------------------------------------------------------|----|

| 4.13 | CAM unit analysis table                                                 | 55 |

| 4.14 | The suggested CAM design is compared to current QCA and CMOS technology | 56 |

| 5.1  | Computational Table of Ex-OR gate                                       | 60 |

| 5.2  | PG circuit with latency analysis                                        | 63 |

| 5.3  | Computational table of PC circuit                                       | 64 |

| 5.4  | Parameters comparison analysis of Parity generator and checker circuit  | 66 |

| 5.5  | Latency analysis of 2:1 multiplexer                                     | 68 |

| 5.6  | Truth table of 4 to 1 multiplexer                                       | 69 |

| 5.7  | Latency of 4:1 mux                                                      | 69 |

| 5.8  | Comparison of new multiplexer design with literature designs            | 71 |

| 5.9  | Computational table of ALU                                              | 74 |

| 5.10 | Comparative analysis results of ALU                                     | 75 |

### **LIST OF FIGURES**

| Figure No. | Title of Figure                                                                                                                                                                                                                     | Page<br>No. |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.1        | Schematic of basic GDI-CMOS based gate                                                                                                                                                                                              | 6           |

| 2.2        | NoT needed for GDI-CMOS and conventional CMOS based logic technique                                                                                                                                                                 | 7           |

| 2.3        | An n x n architecture of (a) reversible gate (b) conservative reversible gate.                                                                                                                                                      | 8           |

| 2.4        | Basic of Quantum cost                                                                                                                                                                                                               | 9           |

| 2.5        | Logical and Physical reversible approach in digital hardware system                                                                                                                                                                 | 10          |

| 2.6        | Basic QCA Cell (90 <sup>0</sup> cell)                                                                                                                                                                                               | 12          |

| 2.7        | Basic types of QCA technology (a) QCA wire $(90^{0})$ (b) QCA<br>Inverter (c) Input Majority Gate (d) 2 input QCA AND Gate<br>realized using 3- input Majority Gate (e) Input QCA OR Gate<br>realized using 3 inputs Majority Gate. | 12          |

| 2.8        | A component of QCA (a) Rotation based $45^{\circ}$ and $90^{\circ}$ wires (b)<br>Inverter (c) 3-input Majority Gate (d) 5-input majority gate (e)<br>Synchronized AND, OR gate (f) Unsynchronized AND, OR gate.                     | 14          |

| 2.9        | Four-phase clock in QCA                                                                                                                                                                                                             | 15          |

| 2.10       | Elements (a) inverter (b) ANC (c) Domain wall (d) corner (e) via type (f) t type (g) x connection (h) pad type (i) fixed '0' (j) fixed '1'                                                                                          | 17          |

| 2.11       | Minority voter gate schematic and layout                                                                                                                                                                                            | 18          |

| 3.1        | Quantum circuit of (a) F2G (b) FRG (c) R-CQCA                                                                                                                                                                                       | 22          |

| 3.2        | The proposed design of reversible multiplexer                                                                                                                                                                                       | 24          |

| 3.3        | Physical design                                                                                                                                                                                                                     | 27          |

| 3.4        | The outcome of a 2:1 multiplexer simulation using R-CQCA                                                                                                                                                                            | 28          |

| 4.1        | CAM cell architecture (a) Block representation (b) Logic circuit                                                                                                                                                                    | 34          |

| 4.2        | CAM cell modules (a) Memory operation unit of a single layer<br>CAM cell logic circuit (b) Match unit of a single layer CAM cell<br>logic circuit                                                                                   | 35          |

| 4.3        | Design of proposed structures using the GDI-CMOS technique (a) Memory operation unit, (b) Match operation unit, (c) CAM cell                                                                                                        | 37          |

| 4.4        | Simulations of proposed structures using the GDI-CMOS techniqu<br>(a) Proposed Memory operation unit, (b) Proposed Match operatio<br>unit, (c) Proposed CAM cell                                                                    | 38          |

| 4.5        | Design of proposed schematic and layout using a QCA technique<br>(a) Memory operation unit, (b) Match operation unit, (c) CAM cell                                                                                                  | 40          |

| 4.6        | Simulations of proposed structures using a QCA technique (a)<br>Memory operation unit (b) Match operation unit, (c) CAM cell                                                                                                        | 42          |

| 4.7  | Graphical Representation of energy analysis, comparison of<br>proposed CAM cell based on QCA technology with prior works<br>[12,19] | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.8  | Temperature deviation with Polarization graph for Proposed QCA-CAM                                                                  | 44 |

| 4.9  | Graphical representation of Performance Comparison between<br>Proposed CAM cell Based on GDI-CMOS and QCA technology                | 45 |

| 4.10 | Graphical representation of performance comparison between<br>newly CAM cell based on GDI-CMOS and QCA Technology                   | 47 |

| 4.11 | Matching unit (a) logic (b) Minority (c) structure (d) outcomes                                                                     | 50 |

| 4.12 | Memory (a) logic-level (b) Minority (c) structure (d) outcomes                                                                      | 52 |

| 4.13 | The new CAM (a) logic (b) Minority (c) layout (d) outcomes                                                                          | 54 |

| 5.1  | New Ex-OR gate (a) Schematic (b) pNML (c) Physical design                                                                           | 60 |

| 5.2  | Outcomes of the Ex-OR                                                                                                               | 60 |

| 5.3  | New PG (a) Schematic (b) block diagram (c) architecture                                                                             | 62 |

| 5.4  | Simulation result of PG using nano-magnetic pNML                                                                                    | 63 |

| 5.5  | The new PC circuit (a) Block diagram (b) schematic (c) physical design                                                              | 65 |

| 5.6  | Simulation result of PC using nano-magnetic pNML                                                                                    | 66 |

| 5.7  | The proposed 2:1 mux circuit (a) Block diagram (b) schematic (c) physical design                                                    | 68 |

| 5.8  | Simulation result of 2:1 mux using nano-magnetic pNML                                                                               | 68 |

| 5.9  | The new 4:1 mux circuit (a) Block diagram (b) schematic (c) Layout                                                                  | 70 |

| 5.10 | Simulation result of 4 to 1 mux using nano magnetic pNML                                                                            | 70 |

| 5.11 | The new ALU (a) Block diagram (b) schematic(c) physical                                                                             | 74 |

| 5.12 | Simulation result of ALU using nano-magnetic pNML technology                                                                        | 74 |

|      |                                                                                                                                     |    |

# List of Symbols and Abbreviations

| Symbol/Abbreviation | Representation/Explanation                         |

|---------------------|----------------------------------------------------|

| VLSI                | Very large-scale integration                       |

| NoT                 | number of transistors                              |

| GDI                 | Gate diffusion input                               |

| CMOS                | Complementary metal oxide semiconductor            |

| mv                  | minority voter                                     |

| F2G                 | Feynman double gate                                |

| R-CQCA              | Reversible-Conservative quantum-cellular- automata |

| CNOT                | controlled NOT gate                                |

| TG                  | Toffoli Gate                                       |

| FRG                 | Fredkin Gate                                       |

| GC                  | Gate count                                         |

| GO                  | Garbage output                                     |

| QC                  | Quantum cost                                       |

| UD                  | Unit delay                                         |

| RAM                 | Random access memory                               |

| QCA                 | Quantum dot cellular automata                      |

| CAM                 | Content-addressable memory                         |

| NML                 | Nanomagnetic Logic                                 |

| pNML                | Perpendicular nano-magnetic Logic                  |

| iNML                | in-plane nano-magnetic Logic                       |

| PMA                 | perpendicular magnetic anisotropy                  |

| MAJ                 | Majority Gate                                      |

| R/W                 | Read/Write                                         |

| EDA                 | Electronic design automation                       |

| ALU                 | Arithmetic logic unit:                             |

| PG                  | Parity Generator                                   |

| PC                  | Parity Checker                                     |

| VH                  | Very high                                          |

| NI                  | No improvement                                     |

| PG\ PC              | Parity generator\ parity checker                   |

| Ex-OR               | Exclusive OR                                       |

## DESIGN, SYNTHESIS AND APPLICATION OF REVERSIBLE LOGIC ARCHITECTURES FOR ENERGY-AWARE SUSTAINABLE COMPUTING

#### Nirupma Pathak (MUIT0118190002)

#### ABSTRACT

With the spectacular rise of processing speed and high-density circuits, the design of low power based architecture has sparked enormous attention. Traditional digital circuit design is based on irreversible computing, which further reduces processing speed and results in substantial energy consumption. Technology such as reversible logic based nano-circuits, which employ qubit based computing, have been developed as a solution for next-generation computing circuit applications and energy-conscious circuits, with a focus on high-speed computing and low energy dissipation. Reversible computing-based circuit technology reboots the input logic depending on the output node for backward calculation.

As part of this dissertation effort, the reversible conservative multiplexer circuit is synthesised, which is the first contribution. A substantial amount of literature work in reversible computing-based multiplexer circuits has been created, however, the optimal multiplexer circuit has not been presented. However, in the literature, a conservative logic-based multiplexer circuit for testing purposes has been introduced. To verify the design of a conservative reversible multiplexer in a physical environment, QCA technology is employed. This suggested conservative reversible multiplexer has been improved in terms of reversible parameters.

CAM memory are the essential components that are utilised as cache memory and match logic units in very high-speed search calculations that may be completed in a single clock cycle, or parallel. The design of an efficient CAM memory architecture is the subject of this dissertation's second chapter. The suggested CAM cell design has two blocks, which are referred to as the memory and the matching unit. Additional to this, both the blocks memory and the matching unit have been implemented in QCA and pNMLtechnology to fully meet the requirements of the high-speed nano-electronics computing application.

The following are some of the unique contributions in this dissertation work:

i A cost-effective conservative reversible multiplexer circuit is introduced that meets the requirements of the quantum world, such as a low value of quantum cost, ancilla input, and a unit delay. It is shown that the suggested conservative reversible multiplexer circuit can be constructed in QCA technology and that is compared to the current work design costs, such as cell count and latency, and found that reduced parameters, when compared to the current work, and the suggested conservative reversible multiplexer circuit outperforms it.

- **ii** A modular design algorithm for a conservative reversible m:1 multiplexer is presented, as is a method for implementing the algorithm.

- **iii** A new idea based on molecular-QCA and pNML technology is presented in the form of a synthesis of the CAM memory system. Additional comparisons with existing circuits demonstrated a significant improvement in practically all parameters when compared to the current circuits. To compare the current state of a QCA measure to a previous state, all primary QCA measures are employed, including the total number of cells, number of majority gates, latency (number of clock cycles), and area. Measurements such as bound box area and clock cycle delay are taken into account in the pNML technology to compare the proposed CAM structure. Based on our comparison results, the recommended form of CAM memory as stated is more likely to meet the criteria of an optimal circuit for nano-computing applications, as seen in the figure cost is one of the important parameters.

- iv Digital circuits based on the pNML technology for use in nanoelectronics applications, including the parity generator and checker, as well as the ALU for robust design is introduced. The objective is to develop a framework for optimising pNML designs to employ a less number of magnets while yet being flexible enough to be used in complex system designs in the future. Following the completion of this synthesis, the new design is suitable for use in the fabrication of nano-electronics circuits. The MagCAD tool was used to check the digital circuits in the synthesised designs before they were implemented. In this work, the major purpose is to construct a robust ALU design in terms of bounded box area and other cost primitives. When comparing the outcomes of these studies. It was found that the use of unique digital designs produces superior results and results in a more robust architecture when compared to the literature works.

#### ACKNOWLEDGMENT

First and foremost, I would want to express my profound gratitude to Dr. Santosh Kumar. I couldn't have asked for a better supervisor than the one I have now. Working with and with Dr. Santosh Kumar was a fascinating and rewarding experience. I'm grateful to have had the opportunity to work with someone of this calibre.

I extend my sincere thanks to Mrs Neeta Rastogi, Head of CSE Department and Er. Puneet Shukla, Deputy head of CSE department in SR Institute of Management & Technology, Lucknow for their sincere cooperation and motivation.

A special thank you to Dr. Bandan Kumar Bhoi, Assistant Professor at VSSUT in Odisha, who has been a tremendous help in assessing my research articles and has earned my highest regard and thanks. I have a debt of gratitude to him for his inspiring leadership, sound advice, never-ending support, and tireless efforts in examining my work. For his continuous encouragement, sound advise, and constant prodding, I owe him a debt of appreciation. As a result of his advice, tools demonstrations, understanding, and observations on quantum circuits and nano-magnetic logic, I am certain that this study will take the appropriate path.

I extend my sincere thanks to Dr. Neeraj Kumar Misra, Assoc Prof., at BIET Hyderabad for their valuable discussion all the time.

I wish to thank my all colleagues and friends of the Maharishi University of Information Technology, Lucknow for their cooperation and encouragement.

An interesting and fun-filled environment to study and grow has been provided to me by the support of my research colleagues. Er. Beer Singh, the head of the ECE at the SR Institute of Management & Technology, has been particularly helpful in this endeavour.

Not to be forgotten is the continuous encouragement and support I received from my loved ones and friends during the course of completing this thesis. The time that my husband, Dr. Neeraj Kumar Misra, and my son, Vedant Misra, have given up to serve our homeland has been priceless to me, and I want to convey my gratitude to them both. Without their invaluable cooperation, this project would not have been able to take place. thank you to God for raining his blessings on me, and I'd also like to convey my thankfulness.

(Nirupma Pathak) MUIT, Lucknow

#### CHAPTER 1

#### **INTRODUCTION**

The approach of scaling in MOS transistors is confined due to physical limits in device performance and manufacturing as per Sadhu et. al [1], which makes it difficult to use. Because of its fast processing speed and low power consumption, it is an excellent choice. digital logic circuits based on dynamic logic and fewer transistors play an essential role in current computer systems as per Khan et. al [2]. One possible option may be quantum-dot cellular automata (QCA) technology, which is based on nano-computing. As a result of its high packing density, high-speed nano-technology approach, and promisingly decreased power consumption during computing, this QCA technology is a viable choice for nano-circuit fabrication and has the potential to replace traditional MOS technology as per Roy et. al. [3]. QCA technology is being utilized to develop low-power circuits and to reduce power consumption in nano-circuit applications, which is a significant step forward. The ultimate objective is to construct nano-circuits using QCA technology in Gaussoumi et. al [4]. QCA is an emerging nano-technology approach for manufacturing circuits at the nano-scale level as per Wang et. al. [5]. QCA based circuit synthesizes with very low power consumption, high computation, and high complexity in a compact chip footprint.

Miniaturization in the direction of high computation in VLSI is a difficult element to overcome for next-generation products. The core of non-magnetic technology must be understandable to the creators of developing technologies in Riente et. al. [6]. Digital circuits need increased processing speed while simultaneously decreasing circuit complexity and power consumption in Sai et. al. [7]. Nano-magnetic logic (NML) is an emerging technology that implements such an architecture at the nano-scale and therefore appears as a potential alternative to the CMOS-VLSI architecture in Breitkreutz et.al. [8]. As the scaling of logic circuits continues to reduce, there is an increasing demand for alternative technologies to fill the gap. NML is a viable alternative that has piqued the curiosity of a large number of academics and researchers as per Cofano et.al [9]. The reduction of circuit density and speed is driving the development of new research parameters for high-speed logic designs. A new nano-technology approach based on nano-magnetic logic circuits has been created, and it is described here. As a result, this technology has the possibility of combining logic computation with storage in the same device, indicating that it has significant potential for use in new technologies in Pala et. al. [10]. Because NML technology is fast nearing its lowest feature size, highest device density, and ability to operate at room temperature, it is becoming more popular as per Breitkreutz et. al. [11]. NML based devices that use less power, integrated devices with high device density, and minimal leakage are all important characteristics of the NML technology as per Bhoi et.al. [12]. A nano-magnetic tool was developed by ToPoliNano (TOrinoPOLLItecnico Nanotechnology) names as MagCAD as per Riente et. al. [6]. For this study, NML technology is separated into two categories: in-plane NML (iNML) and perpendicular NML (pNML). Magnetic anisotropy serves as a criterion for distinguishing between these two categories. The advantage of using an NML-based logic circuit is that it consumes very little power and can be used at room temperature as per Causapruno et.al. [13]. The classification of iNML and pNML is based on the direction of the magnetic field. It is referred to as iNML if the magnetic orientation is in-plane; however, it is referred to as pNML if the magnetic orientation is perpendicular to the plan in Riente et. al. [14]. The pNML category of the NML family is more efficient in terms of having a smaller footprint area and using much less power.

#### **MOTIVATION**

The shrinking of the MOS transistor becomes a key task at a given stage in the production process. QCA technology is a new nano-scale alternative that is gaining popularity as per Kamrani et. Al. [15]. In nano-technology, QCA is focused on high speed and low power consumption in computing, making it a feasible alternative to CMOS technology. QCA is a revolutionary computer technology that offers advantages such as lower power consumption and faster processing speed as per Seyedi et. al. [16].

As scaling down advances at a rapid pace, the need for an alternate semiconductor device to replace standard CMOS technology develops. Because of its high device density and fast processing speed, NML has received a great deal of interest among the alternatives. NML technology is distinguished by its low-power processing, high device density integration, and zero leakage, among other characteristics as per Gypens et. al. [17]. It is necessary to understand how perpendicular nano-magnetic logic (pNML) works to build circuits that function as digital logic. CMOS technology is being phased out in favour of NML-based digital logic devices, which are becoming more common as per Mattela et. al. [18] All of the distinguishing characteristics of reversible logic, QCA, and NML technologies encourage the development of a nanocircuit based on emerging technology in the domain of nano-computing.

#### **OBJECTIVE**

Making a multiplexer is a complicated task, and thinking about the structure and architecture of the design in the context of reversible logic involves requires a significant amount of paper effort. Existing research efforts on reversible multiplexer architectures are missing in rigour and comprehensiveness, and this has to be addressed. According to previous research, the proposed reversible multiplexer has a lower overhead in terms of quantum cost when compared to the existing work.

Making CAM memory in QCA and pNML technologies is a very tough undertaking. The proposed CAM architecture is compared to various earlier studies on CAM memory, and the findings show that our approach outperforms existing techniques in terms of design parameter overhead for a wide range of test circuit types. The proposed CAM memory as compared to relatively recent research, and it was determined that the proposed work was better in every way. Circuit designs such as a reversible multiplexer and CAM memory in the QCA method are recommended for use in the era of nano-computing since they are cost-effective and provide a benefit.

The suggested pNML-based ALU architecture is very robust in terms of latency and area, and it is also highly efficient. It has been determined that the ALU layout design in pNML

technology is the most suitable for creating efficient circuits. Comparing the results of this study to earlier work, the researchers discovered a significant decrease in the pNML parameters in terms of latency and area for several benchmark samples. Through the use of a variety of methodologies, this thesis proposes an efficient digital circuit architecture that strives to bridge the gap between architectural reality and design completeness.

#### METHODOLOGIES OF THE RESEARCH

Presented in this dissertation work is an advanced architecture consisting of reversible multiplexers, CAM memory, parity generators, parity checkers, and arithmetic logic units (ALUs), all of which are physically implemented. Each one of the suggested architectures is distinct and cost-effective so that it is suitable for energy-aware sustainable computing.

Steps that are followed during the research are described below:

- Gaining an understanding of the reversible R-CQCA gate and using this conservative reversible gate to synthesize and conservative reversible multiplexers design.

- Understanding the memory and match logic block and with this blocks synthesis the CAM memory block.

- The half adder, OR, Ex-NOR, AND multiplexers are all represented in the pNML layout; understanding this arrangement, and designing the pNML layout of the ALU is the next step.

#### THESIS ORGANIZATION

This section provides a high-level summary of the dissertation. A foundational section of the dissertation is provided to assist readers in comprehending the terms used throughout the dissertation. As part of determining the superiority considerations for the planned research, the associated state-of-the-artwork, as well as its issues and limitations, is examined. This dissertation is split into five chapters, each of which is labelled with the numbers 1 through 5.

#### Chapter 1

The essential notion of this dissertation work is discussed in Chapter 1. The overview of this dissertation work are included a short explanation of motivation, aim, methodology, work outline, and thesis arrangement.

#### Chapter 2

The second chapter provides a basic review of several technologies such as GDI-CMOS, reversible logic, quantum computing, QCA, and pNML.

#### Chapter 3

This chapter covers the synthesis technique, simulation results, and design parameters for the conservative reversible multiplexer.

#### **Chapter 4**

The design technique for content addressable memory based on QCA and pNML technologies are discussed in this chapter.

#### Chapter 5

Using nano-magnetic logic technology, Chapter 5 comprises different digital logic circuits such as parity generators, parity checkers, multiplexer and ALUs.

#### **1.4 CONCLUSION**

This chapter, after presenting reversible logic, quantum technology, QCA and pNML technology, as well as their methodology of the work. A detailed description of the structure of this thesis is also provided.

#### CHAPTER 2

#### FUNDAMENTAL AND STATE-OF-ART-WORK

# FUNDAMENTAL OF GDI, REVERSIBILITY CONCEPT, QUANTUM TECHNOLOGY, QCA AND NANOMAGNETIC TECHNOLOGY

In today's nano-electronics system design, one of the fundamental problems is to create a cost-efficient product, while also using less power in Shahidi, et. al. [19]. However, the best possible power value is achieved without sacrificing speed, area, or high-performance applications in the process. This is geared at the use of modern technologies. This is to say that, the next generation of nano-electronics applications in quantum technology represents a completely novel technology as per Pallav et. al. [20]. Power dissipation correlated to heat dissipation is a critical restriction of electronic equipment. Overheating, information loss, and, in certain situations, component failure is all consequences of power loss in electronic systems in Dmitri et.al. [21]. The transistor count in integrated circuits is doubled every two years, according to Moore's law of exponential growth. The amount of power needed by a device is directly proportional to the amount of heat lost by that device, and the greater the number of components a device has, the more power it needs in Gerhard et. al. [22]. The higher device density used by the device means it greater the amount of heat dissipated. In other words, if the power expended by a device is more than the power required by the device's design, the heat created will not be able to be quickly dispersed, resulting in overheating. Overheating may cause component failure and, in the worst-case scenario, partial or complete failure of the device in Adriano et. al. [23]. In electronic systems, a reduction in the amount of heat dissipated by the system provides an advantage in terms of high densities and speeds while maintaining no loss of information in Jurcevic et.al. [24]. Since the early 1990s, several low-power approaches have been developed and used to overcome the limitations of CMOS semiconductor technology. For this reason, various quantum nanotechnologies have evolved in which quantum gates are widely accessible in Kwon et. al. [25].

As per famous R. Landauer's principle [26] drawn that logically irreversible systems, which erasure of a logic-bit is always associated with a high value of the entropy. For the system to function properly during calculation, all of the erased logic bits in the system must dissipate about kTln2 of heat, where k is Boltzmann's constant and T is the absolute temperature at which the process is carried out. To be reversible, Bennett [27] the principal, has determined that an energy-free computing system is required C.H.Bennett et. al. Quantum Computing uses the concept of "Quantum mechanics" of superposition and entanglement through quantum gates, which are reversible both physically and logically, thereby reducing loss of power in electrical systems in Hevia et. al. [28]. This chapter deals a fundamental of some of the fundamental details about GDI, reversible computing, QCA computing, quantum computing and nano-magnetic logic.

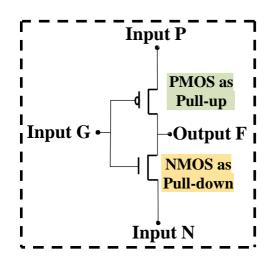

#### **Basics of GDI-CMOS Technique**

Gate diffusion input (GDI) based cell consists of two transistors of type P-MOS and N-MOS and is almost similar to the CMOS inverter as shown in Fig 2.1. A GDI cell contains three inputs, which are denoted by the letters G, P, and N, as per Ponnian et.al. [29]. Input G means gate, which is associated with both NMOS and PMOS type transistors. The P is an input signal, which can either be the source/drain of the PMOS transistor. The N is input-signal which can either be the drain/source of NMOS transistor.

Fig. 2.1 Schematic of basic GDI-CMOS based gate

Both PMOS and N-MOS type transistor bulks are connected to nodes N and P respectively. The input nodes, P and N can be biased random depending on the function of the cell. The main dissimilarity between the CMOS inverter and the GDI basic cell is that in the CMOS inverter, the P-MOS drain is associated with the input-power and the N-MOS source is grounded while that in GDI cell, the inputs, G, P and N can be given to power supply or can be grounded or taken as input depending on the function of the circuit. This effectively decreases the number of transistors for implementing basic logic circuits and different complex functions compared to its CMOS implementation.

#### **Implementation of Different Functions using GDI-CMOS Technique**

GDI-CMOS is a very fundamental cell because of its simplicity and ability to generate basic logic operations like AND, OR, MUX, inverter, and XOR as per Krishna et.al. [30]. The three input GDI cell based on PMOS and NMOS transistor is shown in Fig 2.1. It can be seen that the GDI cell consists of three inputs nodes like K, L and M at nodes G, P and N, respectively. By setting the configuration of the input nodes as Gate (G), P diffusion (P) and N diffusion (N) in the GDI cell, various logical operations can be performed as shown in Table 2.1. The output logic is dependent on the input node values in the GDI cells of the inputs. Table 2.1 presents the logic operation based on a GDI cell by setting inputs. Many functions can be realized using the GDI technique by changing nodes G, N and P inputs of GDI cell given in Table 2.1 accordingly while using fewer transistors compared to CMOS implementation. GDI cell has three nodes G, P and N and node inputs are denoted as K, L and M respectively.

| Operation of GDI cell | No of transistors | Node G | Node P | Node N |

|-----------------------|-------------------|--------|--------|--------|

| OR logic              | 2                 | K      | L      | High   |

| AND logic             | 2                 | K      | Low    | М      |

| MUX logic             | 2                 | K      | L      | М      |

| NOT logic             | 2                 | K      | High   | Low    |

| XOR logic             | 4                 | K      | L      | L      |

**Table 2.1.** Generating of basic operations using the GDI cell

Note: K means-input at node G, L means-input at node P, M means-input at node N, High means-DC Supply VDD, Low means-Ground Gnd

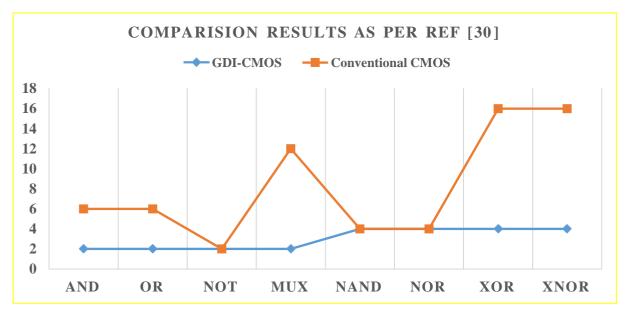

#### Comparison between GDI-CMOS and conventional CMOS logic gates transistors

Fig 2.2, shows a comparison of the number of transistors (NoT) needed for the various logic functions created using the GDI approach and CMOS technology. NoT is reduced using the GDI technique for different logic functions compared to that of CMOS logic gates as per Krishna et. al. [30]. The above basic GDI-CMOS logic gates are used for building any logic circuits.

Fig.2.2 NoT needed for GDI-CMOS and conventional CMOS based logic technique

#### **Fundamentals of Reversible Computing**

Using the notion of "Second law of Thermodynamics," reversibility is shown in nature. This law asserts that if any system is reversible, then the entropy of that system remains constant. When the entropy of a system remains constant, no heat is dissipated in the system as per Singh et.al. [31]. For a system to be reversible, it must be in a state of equilibrium. Consequently, if the reversible principle is applied to the circuit design, there will be no heat dissipation, resulting in no power loss in the system as per Gaur et. al. [32]. It is necessary to design at two major subsystem levels when developing a reversible digital electronic system, namely the gate level designing and the transistor level designing. All of the components of a digital electronic system, including the logic and physical hardware, should be reversible. As a result, the reversibility notion must be implemented at both the gate and transistor levels to

create energy-efficient, recyclable digital systems or circuits that do not produce heat or lose information as per Saeedi et.al. [33].

**Definition 2.1.** It is necessary to have an equal number of inputs  $I_v(A_0, A_1,...A_n)$  and outputs  $O_v(B_0, B_1,...B_n)$ , as well as the bijective mapping, as illustrated in Fig. 2.3 (a) of the reversible gate.

**Definition 2.2** A conservative, reversible gate is defined as one in which the hamming weight of the inputs and outputs is equal, as seen in Fig 2.3 (b). A more acceptable representation would be in the form of an equation (2.1).

(a)

Reversible Gate

$$A_1$$

$A_2$

$A_n$

$A_n$

$A_n$

$B_n$

$B_n$

$$A_1 \oplus A_2 \oplus \dots A_n \xleftarrow{\text{bijective}} B_1 \oplus B_2 \oplus \dots B_n$$

(2.1)

**Definition 2.3.** The significant cost-metric parameter for reversible logic is quantum cost. Any reversible gate can be decomposed into 1 x 1 and 2 x 2 gates such as CNOT, V and V<sup>+</sup> gates (called quantum primitive gates).

The CNOT gate is depicted in Fig. 2.4 (a) and the quantum cost calculation for some basic structures are depicted in Figs. 2.4 (b), 2.4 (c), 2.4 (d), 2.4 (e). The cost is calculated by counting total primitives gates. The controlled V and V<sup>+</sup> gates are depicted in Fig. 2.4 (f). In the controlled V gate when the control input A=1, implies Q=V(B), that V is synthesized by equation 2.2. When A=0, implies Q=B, where A and B are inputs and Q is the output. The V and V<sup>+</sup> gates have some basic properties that are drawn in equations (2.3) and (2.4).

The quantum cost parameter is a cost-metric parameter that is important for reversible logic. Any reversible gate, such as the CNOT, V, and V+ gates, can be divided down into two types of quantum gates:  $1 \times 1$  and  $2 \times 2$  gates (called quantum primitive gates) as per Große et.al. [35]. The CNOT gate is depicted in Fig. 2.4 (a) and the quantum cost calculation for some basic structures are depicted in Figs. 2.4 (b), 2.4 (c), 2.4 (d), 2.4 (e). The cost is computed by adding up the entire number of primitive gates. The controlled V and V+ gates are shown in Fig. 2.4 (f). When the control input A=1, which means Q=V(B), the V gate is synthesised by equation 2.2 in the controlled V configuration. When A=0, Q=B is implied, where A and B are the inputs and Q is the output of the equation. The V and V+ gates have several fundamental qualities that are shown in equation (2.3), as well as in equation (2.4).

$$V = \frac{i+1(1 - i)}{2(-i - 1)}$$

(2.2)

| $V \ge V^+ \ge V^+ \ge NOT$                                                                | (2.3) |

|--------------------------------------------------------------------------------------------|-------|

| $\mathbf{V}^{+} \mathbf{x} \mathbf{V} = \mathbf{V} \mathbf{x} \mathbf{V}^{+} = \mathbf{I}$ | (2.4) |

Fig. 2.4 Basic of Quantum cost

#### Logical-Reversibility

The number of outputs on reversible logic gates is the same as the number of inputs. When it comes to reversible logic gates, there is an equal number of one-to-one mappings between input vectors and output vectors, which means that inputs can be recovered using outputs and the reverse is true. Except for the NOT gate, no other logic gate is reversible. Reversible gates get balanced functions at the outputs if inputs don't have any constants as per Jamal et. al. [35]. If some of the inputs of reversible gates have constants, then outputs can have unbalanced functions with extra inputs and garbage outputs (outputs that are not important for the execution of the function) depending on the functionality of reversible gates. Several novel reversible logic gates are TG, FG, and FRG gates to use the reversible gate based quantum circuit design as per Jamal et. al. [35].

#### **Physical-Reversibility**

Physical reversibility is achieved by making design reversible. If any system at the device level doesn't have any energy loss while running the system backwards, then the system is said to be physically reversible. To achieve physical reversibility, adiabatic logic is applied to CMOS circuits. The adiabatic circuit gives stored energy or RC across the load capacitance back to the Power clock's purpose is to not turn "transistor on" when voltage is across it and not turn "transistor off" when current is flowing through it. If we maintain the above conditions in all phases in the slow movement, then the restore phase will recover energy back to the power clock. This helps in restoring energy without loss when the system or circuit run backwards. Using Reversible logic gates and applying adiabatic logic to any CMOS circuit can help in reducing power and heat. But adiabatic CMOS circuits have disadvantages because of slow speed and high area overhead. Technologies such as QCA, Magnetic spin devices, adiabatic CMOS, and nano-magnetic (pNML or iNML) have succeeded in quantum computing technology for physical reversibility. The many steps of digital hardware are shown in the flow chart shown in Fig. 2.5; the logical reversibility is presented in the fifth level, and the physical reversibility is presented in the sixth level, respectively as per Sridharan et. al. [36].

#### **Quantum Technology and Quantum gates**

Logic computations, sensing, imaging, and simulations are all made possible by quantum technology, which is a promising developing technology that makes use of the notion of quantum physics. Quantum technology is the application of quantum physics ideas like tunnelling, entanglement, and superposition.

In quantum computing, quantum circuits are constructed using quantum gates, which are reversible and operate on "qubits," which are small units of information. Qubits are used in quantum computing for retracing information because they are entangled (sealed) when they enter a quantum gate and they preserve their entangle when they come out of a quantum gate as per Fredkin et. al. [40]. Quantum gates are reversible devices that allow for the retracing and restoration of information. A unitary matrix may be used to represent quantum gates to simplify their representation. In a quantum gate, the input qubits and the output qubits are the same as one another. In contrast to classical gate states, which may only be either 0 or 1, quantum gate states or vectors are referred to as "kets," and they can be either 0 or 1. In the matrix form shown below, a single qubit "p" has two probability kets or vectors associated with it.

Fig. 2.5 Logical and Physical reversible approach in the digital hardware system

$|p\rangle = \begin{bmatrix} V_0 \\ V_1 \end{bmatrix}$ Here, ket for "0" value  $|0\rangle = \begin{bmatrix} 1 \\ 0 \end{bmatrix}$  and ket for "1" value  $|1\rangle = \begin{bmatrix} 0 \\ 1 \end{bmatrix}$

Similarly, two qubits "p and q" have four vectors in a matrix given below.

$$|pq\rangle = \begin{bmatrix} V_{00} \\ V_{01} \end{bmatrix} \begin{bmatrix} V_{01} \\ V_{11} \end{bmatrix}$$

The quantum gates can process complex information computations securely without loss at high speeds with low power compared to CMOS reversible gates, but has more scope for error, making the quantum gate designing the complex. Quantum technology readily offers reversibility, security and highly complex and sensitive computations. There is a lot more to be researched in the future to build an efficient error-free quantum circuit as quantum technology has reduced energy dissipation compared to conventional CMOS technology.

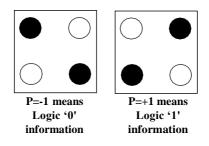

#### **Fundamentals of QCA Technology**

The scaling approach in MOS transistors has several limitations, and it is now experiencing restrictions because of channel length restrictions associated with nanotechnology manufacturing problems and other factors Angizi et. al. [41]. With the progress of technology and improvements, power dissipation has become a critical restriction, which has a negative impact on the performance of portable devices as per Lent et.al. [42]. The use of device power has a significant impact on the performance of portal devices such as mobile phones, sensors, medical equipment, and battery life Pal et. al. [43]. As a result, the device size, weight, and cost of portable systems are restricted. To attain high-performance devices, the clock frequency must be raised, and to deal with the extra heat, a cooling circuit must be included, which in turn increases density to limit power consumption and minimise heat created. The use of QCA technology has been suggested as a potential alternative as per Sasamal et.al. [44].

The QCA technology is a well-known nano-technology that uses majority gates to create logic circuits rather than transistors, so achieving the status of a transistor-less technology as per Misra et.al [45]. A number of its appealing characteristics, including low density, low-power- consumption, fast computing speed, and high scaling over CMOS technology, distinguish it as a future trend technology that may be utilised to construct electronic devices with nano-scale dimensions Teja et. al [46].